續航提升數倍!IBM 5nm制程吊打Intel

目前的芯片制程工藝最先進的非Intel莫屬,Intel在兩三年前就已經實現了14nm FinFET 3D晶體管工藝,并且由于標準不同,即使臺積電和三星量產了10nm制程,實際的效果可能仍然無法完全匹敵Intel的新一代14nm制程。然而這個情況也許會在幾年之后發生逆轉,因為IBM已經開發出了全新的5nm制程工藝,它將延續摩爾定律,采用全新的晶體管結構,克服量子效應帶來的漏電現象,而這是普通3D晶體管無法做到的。

IBM和三星以及AMD的老伙伴Globalfoundries進行合作,他們開發了全新的硅基晶體管制作工藝,使得制程微縮的路線圖從極限的7nm進一步下探到5nm水平。目前,芯片制程工藝發展到14nm,工藝研發難度越來越大,一直保持領先的Intel也不得不多次修改Tick-Tock戰略,面對AMD Ryzen處理器的競爭,他們仍然推出了第四代14nm芯片,可見新工藝研發難度之大。

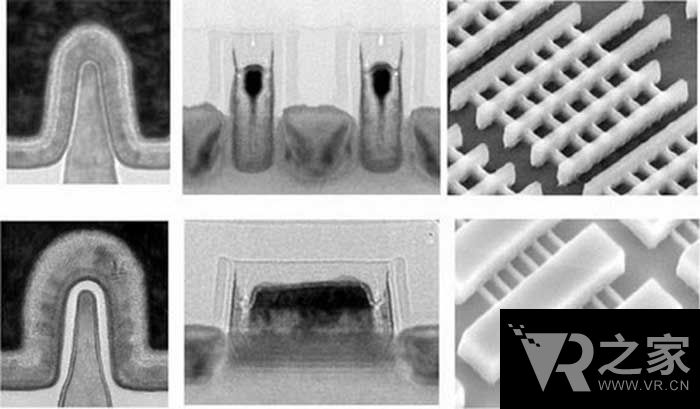

在科學家們此前的預測中,即使采用最新的極紫外光刻機(EUV)人們也只能制作出極限為7nm制程的芯片(目前的14nm芯片仍然是193nm浸入式光刻機),并且晶體管結構已經從普通的2D平面晶體管進化為3D晶體管(鰭式場效應管)。但是在7nm制程以下,鰭式場效應管同樣無法很好地控制晶體管內的電子,而IBM通過采用全新的晶體管結構將制程拓展到5nm。

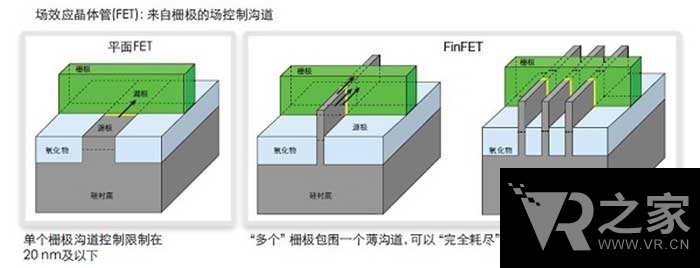

2D平面場效應管,FinFET和FinFET+(水平堆疊)

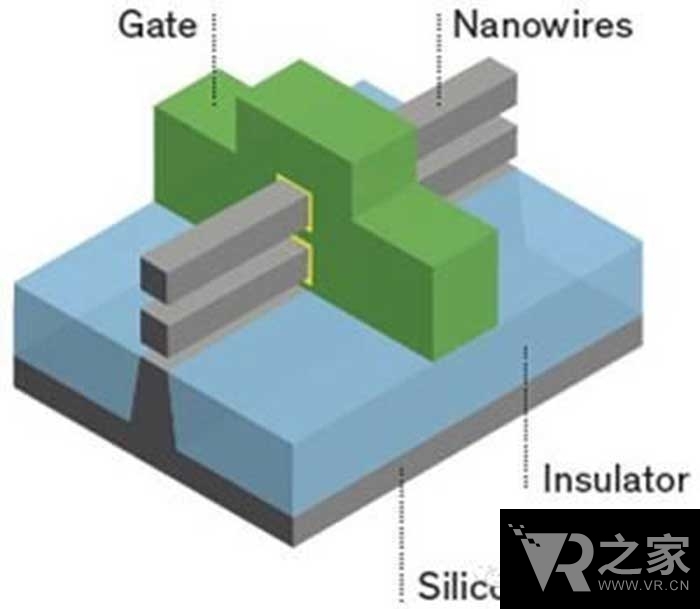

據VR箘了解,場效應管是現代處理器的基礎,由源極、柵極和漏極組成,在2D平面晶體管技術中,源極和漏極分別位于柵極的兩側下方,相互之間并不導通,如果在柵極施加一個電壓,源極和漏極之間就會暫時形成一個溝道,這樣通過施加電壓完成晶體管的通斷。隨著晶體管不斷縮小,源極和漏極之間的距離也越來越近,柵極下方的氧化物絕緣層也越來越薄,電子很容易自動從源極漏過去,也就是所謂的“漏電”;同時柵極的接觸面積也越來越小,導致其對電子通斷的控制力減弱;FinFET通過改變晶體管結構增加接觸面積,增強了柵極的控制能力,使得制程能夠縮小到20nm以下。而最新的納米線場效應管則再一次改變晶體管堆疊方式,使得制程可以再一次縮小而不會進一步降低柵極控制能力。

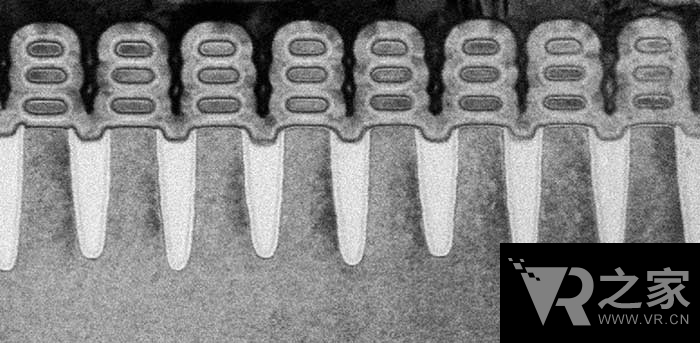

納米線場效應管

當然,盡管新技術從原理上仍然是FinFET的延伸,但關鍵在于它實現了垂直方向的堆疊,如果說水平堆疊是FinFET技術的自然延伸,那么垂直堆疊就需要一些新技術突破才能夠實現了。

FinFET

更先進的工藝能夠到來更低的功耗和更高的性能功耗比,IBM認為該技術能夠進一步推動物聯網和其他數據密集型任務的進化。不過對于普通消費者而言,5nm技術意味著移動電子設備能夠獲得更加優秀的續航表現,我們的智能手機續航能力有望達到目前14nm技術設備的2~3倍。由于目前的智能手機續航能力已經令人基本滿意,或許它更大的作用在于更低的發熱量以及更長的持續高負載運行時間。

納米線場效應管

VR箘認為最能受益于上面提到的兩點的設備應該是二合一平板和VR一體機設備,由Core M處理器驅動的二合一平板在未來可以持續保持2GHz以上的運行頻率,并將發熱控制在合適的程度;而VR一體機也能夠將續航由現在的2小時提升到6小時以上。在高性能領域,5nm制程也將發揮強大的威力,NVIDIA即將發售的“核彈”Tesla V100據稱擁有211億晶體管,核心面積跟Apple Watch表盤一樣大(1080ti只有它的一半),然而5nm制程可以在指甲蓋大小的區域集成300億晶體管,Intel 14nm制程目前只能在指甲蓋大小區域制作出core m級別的處理器。

當然,我們并不可能在最近兩三年內看到實際的商品。事實上,10nm制程的高通驍龍835仍然只有小范圍發貨,而Intel即將發售的8代Core i系列處理器仍然使用了14nm制程(Intel 14nm制程相當于三星10nm制程,但如果繼續縮小制程,兩者在5nm節點都必須采用全新的工藝)。最早的7nm制程芯片有望在2018年正式登場,不過目前來看,顯然采用全新的5nm 納米線晶體管技術的產品更加令人期待。(參考Intel 22nm和32nm,臺積電16nm和20nm之間的差距)

未經授權,禁止轉載,違者必將追究法律責任。

文章點評

相關閱讀

-

PSVR銷量破百萬 VR游戲共售出五百萬款

PSVR銷量破百萬 VR游戲共售出五百萬款里程碑!索尼今日宣布,PSVR設備累計銷售突破100萬套。PSVR的所有者們迄今已經購買了525萬套VR游戲,平均每個游戲玩25分鐘。...

- 你以為它是普通眼鏡?這個AR眼鏡不一般

- 森聲科技將攜3D錄音黑科技亮相CES Asia2017

- E3早知道:唱不了主角的VR還有哪些值得期待

- 《克羅維:沉默的兵工廠》Steam限時打折中

- AR眼鏡即將登陸歐洲市場 照片視頻盡情拍